T flip flop is the simplified version of jk flip flop.

T flip flop characteristic table.

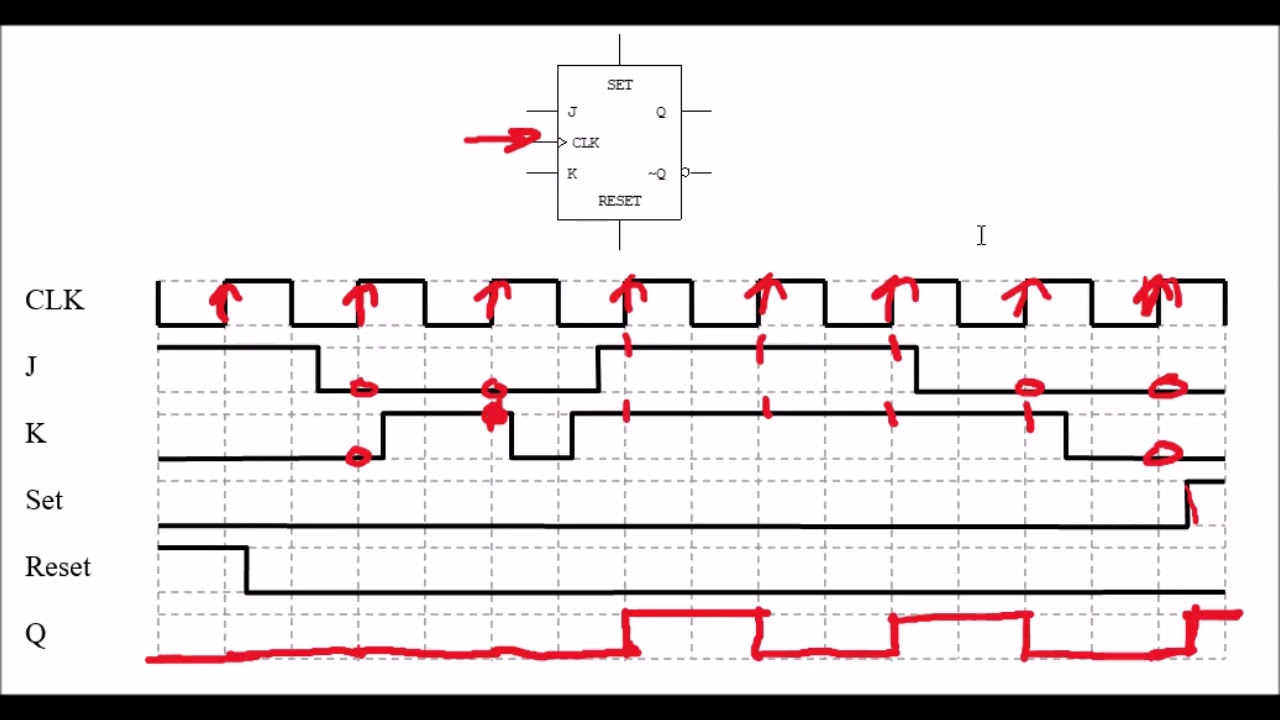

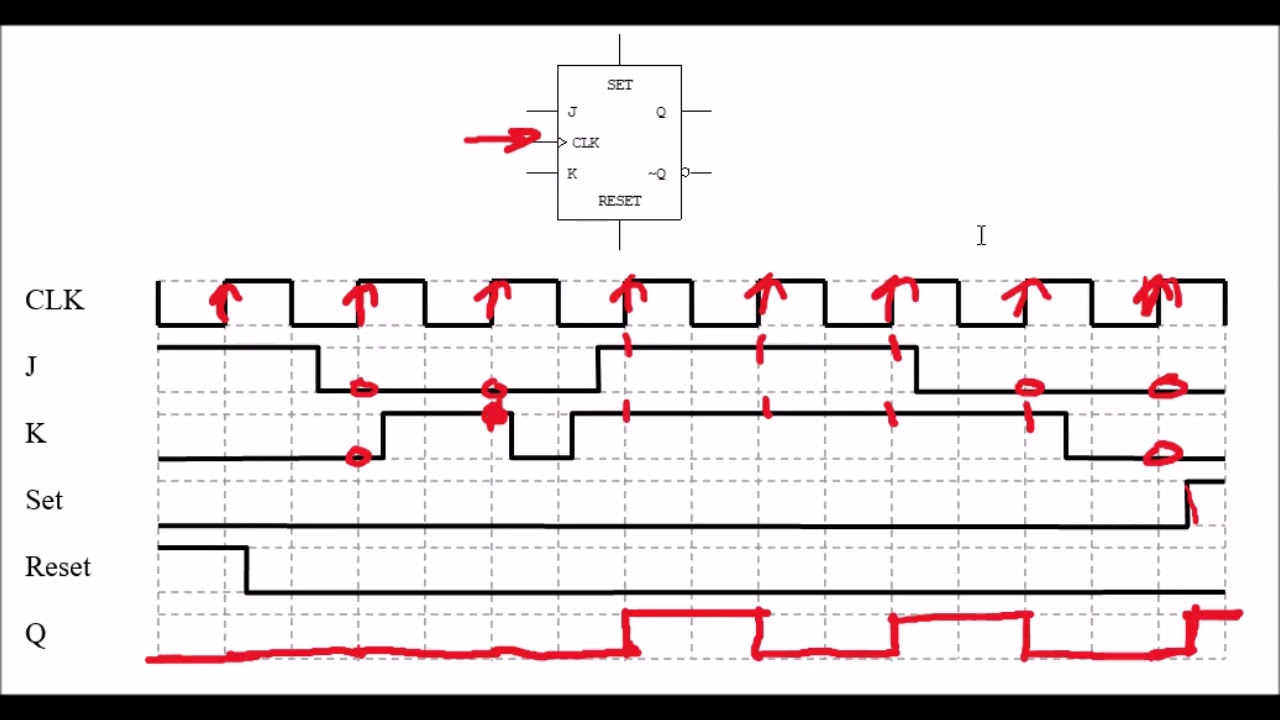

It operates with only positive clock transitions or negative clock transitions.

Jk flip flop jack kilby t flip flop toggle out of the above types only jk and d flip flops are available in the integrated ic form and also used widely in most of the applications.

The circuit diagram of t flip flop is shown in the following figure.

Truth table characteristic table and excitation table for t flip flop contribute.

Basic flip flops in digital electronics.

The truth table of a t flip flop is shown below.

The following table shows the characteristic table of d flip flop along with the excitation input of t flip flop.

In this article let s learn about different types of flip flops used in digital electronics.

Truth table of t flip flop.

Therefore consider the characteristic table of d flip flop and write down the excitation values of t flip flop for each combination of present state and next state values.

Here in this article we will discuss about t flip flop.

Digital flip flops are memory devices used for storing binary data in sequential logic circuits latches are level sensitive and flip flops are edge sensitive.

The next state for the t flip flop is the same as the present state q if t 0 and complemented if t 1.

The characteristic table is useful during the analysis of sequential circuits when the value of flip flop inputs are known and we want to find the value of the flip flop output q after the rising edge of the clock signal.

It is obtained by connecting the same input t to both inputs of jk flip flop.

The name t flip flop is termed from the nature of toggling operation.

Truth tables characteristic equations and excitation tables of different flipflops nand and nor gate using cmos technology circuit design of a 4 bit binary counter using d flip flops.

This modified form of jk flip flop is obtained by connecting both inputs j and k together.

As mentioned earlier t flip flop is an edge triggered device.

If the output q 0 then the upper nand is in enable state and lower nand gate is in disable condition.

It means that the latch s output change with a change in input levels and the flip flop s output only change when there is an edge of controlling signal that control signal is known as a clock signal q.

A t flip flop is like jk flip flop.

These are basically a single input version of jk flip flop.