How would i do this in a vhdl test bench to run through a truth table for a multiplexer.

Test bench truth table.

A single half adder has two one bit inputs a sum output and a carry out output.

Create a test bench and verify your implementation using simulation.

J and k are outputs a b c j k 0 0 0 0 1.

There is also a test bench that stimulates the design and ensures that it behaves correctly.

Truth table of simple combinational circuit a b and c are inputs.

The code creates a half adder.

In this tutorial we will create a simple combinational circuit and then create a test bench test fixture to simulate and test the correct operation of the circuit.

Using vivado to create a simple test fixture in verilog in this tutorial we will create a simple combinational circuit and then create a test fixture test bench to simulate and test the correct operation of the circuit.

Process sel variable p std logic vector 3 downto 0.

Am i on the right track.

Next we will write a testbench to test the gate that we have created.

а d оооооооо oooppppoooom oooooooolo 0 нон орон орон орона h8 h h h 8 o h 8 8 6 8 8 8 8 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1.

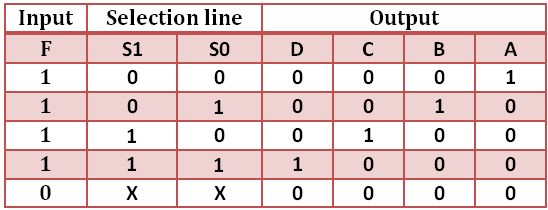

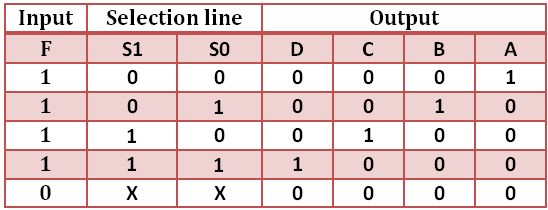

Refer to the truth table below to see how these bits operate.

Save the output waveforms.

Truth table of simple combinational circuit a b and c are inputs.

This code will send different inputs to the code under test and get the output and displays to check the accuracy.

A testbench is an hdl module that is used to test another module called the device under test.

Begin p 0000 for j in 0001 to 1111 loop if j 1111 then p p 1.

A simple truth table will help us describe the design.

Sel 00 after 100 ns 01 after 200 ns 10 after 300 ns 11 after 400.

Testbench is another verilog code that creates a circuit involving the circuit to be tested.